# J174, J175 P-Channel JFET

Technical

Support

#### Features

- InterFET P0099F Geometry

- Low Noise: 8 nV/VHz Typical

- Low Rds(on): 85 Ohms Maximum

- RoHS Compliant

- SMT, TH, and Bare Die Package options.

#### **Applications**

- Choppers

- Commutators

- Analog Switches

#### Description

The 30V InterFET J174 and J175 JFET's are targeted for high gain low noise switching, commutator, and chopper applications.

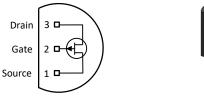

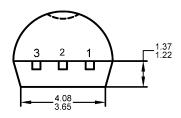

#### **TO-92 Bottom View**

#### **Product Summary**

|                      | Parameters                         | J174 Min | J175 Min | Unit |

|----------------------|------------------------------------|----------|----------|------|

| BV <sub>GSS</sub>    | Gate to Source Breakdown Voltage   | 30       | 30       | V    |

| IDSS                 | Drain to Source Saturation Current | -20      | -7       | mA   |

| V <sub>GS(off)</sub> | Gate to Source Cutoff Voltage      | 5        | 3        | V    |

### Ordering Information Custom Part and Binning Options Available

| Part Number          | Description                            | Case  | Packaging            |

|----------------------|----------------------------------------|-------|----------------------|

| J174; J175           | Through-Hole                           | TO-92 | Bulk                 |

| SMPJ174; SMPJ175     | Surface Mount                          | SOT23 | Bulk                 |

|                      | 7" Tape and Reel: Max 3,000 Pieces     |       | Minimum 1,000 Pieces |

| SMPJ174TR; SMPJ175TR | 13" Tape and Reel: Max 9,000 Pieces    | SOT23 | Tape and Reel        |

| J174COT; J175COT     | Chip Orientated Tray (COT Waffle Pack) | СОТ   | 400/Waffle Pack      |

| J174CFT; J175CFT     | Chip Face-up Tray (CFT Waffle Pack)    | CFT   | 400/Waffle Pack      |

**Disclaimer:** It is the Buyers responsibility for designing, validating and testing the end application under all field use cases and extreme use conditions. Guaranteeing the application meets required standards, regulatory compliance, and all safety and security requirements is the responsibility of the Buyer. These resources are subject to change without notice.

# **Electrical Characteristics**

#### Maximum Ratings (@ T<sub>A</sub> = 25°C, Unless otherwise specified)

|                  | Parameters                                 | Value      | Unit  |

|------------------|--------------------------------------------|------------|-------|

| VRGS             | Reverse Gate Source and Gate Drain Voltage | 30         | V     |

| $I_{FG}$         | Continuous Forward Gate Current            | 50         | mA    |

| PD               | Continuous Device Power Dissipation        | 360        | mW    |

| Р                | Power Derating                             | 3.27       | mW/°C |

| Τı               | Operating Junction Temperature             | -55 to 125 | °C    |

| T <sub>STG</sub> | Storage Temperature                        | -65 to 200 | °C    |

### **Static Characteristics** (@ TA = 25°C, Unless otherwise specified)

|                      |                                       |                                                | J1  | J174 |     | J175 |      |

|----------------------|---------------------------------------|------------------------------------------------|-----|------|-----|------|------|

|                      | Parameters                            | Conditions                                     | Min | Max  | Min | Max  | Unit |

| V(BR)GSS             | Gate to Source<br>Breakdown Voltage   | $V_{DS} = 0V$ , $I_G = 1\mu A$                 | 30  |      | 30  |      | V    |

| I <sub>GSS</sub>     | Gate to Source<br>Reverse Current     | $V_{GS} = 20V, V_{DS} = 0V$                    |     | 1    |     | 1    | nA   |

| V <sub>GS(OFF)</sub> | Gate to Source<br>Cutoff Voltage      | V <sub>DS</sub> = -15V, I <sub>D</sub> = -10nA | 5   | 10   | 3   | 6    | V    |

| I <sub>DSS</sub>     | Drain to Source<br>Saturation Current | $V_{GS} = 0V, V_{DS} = -15V$<br>(Pulsed)       | -20 | -125 | -7  | -70  | mA   |

| Id(off)              | Drain Cutoff Current                  | V <sub>DS</sub> = -15V, V <sub>GS</sub> = 10V  |     | -1   |     | -1   | nA   |

### **Dynamic Characteristics** (@ TA = 25°C, Unless otherwise specified)

|                                   |                                    |                                                                              | J174      |                  | J175         |      |      |

|-----------------------------------|------------------------------------|------------------------------------------------------------------------------|-----------|------------------|--------------|------|------|

|                                   | Parameters                         | Conditions                                                                   | Min       | Max              | Min          | Max  | Unit |

| Rds(on)                           | Drain to Source<br>ON Resistance   | V <sub>DS</sub> <= 0.1V, V <sub>GS</sub> = 0V, f = 1kHz                      |           | 85               |              | 85   | Ω    |

| Cgd                               | Drain Gate<br>Capacitance          | V <sub>DS</sub> = 0V, V <sub>GS</sub> = 10V, f = 1MHz                        | 5.5 (typ) |                  | 5.5 (typ)    |      | pF   |

| Cgs                               | Input Capacitance                  | V <sub>DS</sub> = 0V, V <sub>GS</sub> = 10V, f = 1MHz                        | 5.5 (typ) |                  | 5.5 (typ)    |      | pF   |

| C <sub>gd</sub> + C <sub>gs</sub> | Drain + Source Gate<br>Capacitance | $V_{DS} = V_{GS} = 0V$ , f = 1MHz                                            | 32 (      | typ)             | yp) 32 (typ) |      | pF   |

| t <sub>d(ON)</sub>                | Turn ON Delay Time                 |                                                                              | 2 (1      | :yp)             | 5 (t         | typ) | ns   |

| tr                                | Rise Time                          | J174: $V_{DD}$ = -10V, $V_{GS(OFF)}$ = 12V,<br>R <sub>L</sub> = 560 $\Omega$ | 5 (typ)   |                  | 10 (typ)     |      | ns   |

| t <sub>d(OFF)</sub>               | Turn OFF Delay Time                | J175: $V_{DD}$ = -6V, $V_{GS(OFF)}$ = 8V<br>R <sub>I</sub> = 1200 $\Omega$   | 5 (1      | 5 (typ) 10 (typ) |              | typ) | ns   |

| t <sub>f</sub>                    | Fall Time                          | NL - 1200 12                                                                 | 10 (typ)  |                  | 20 (typ)     |      | ns   |

Technical

Support

Order

Now

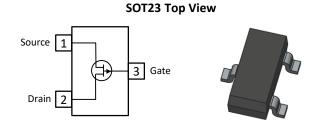

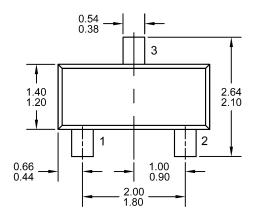

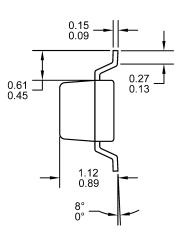

# SOT23 (TO-236AB) Mechanical and Layout Data

### **Package Outline Data**

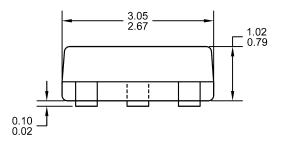

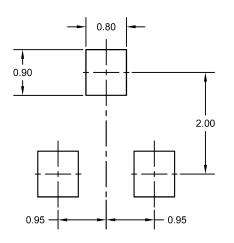

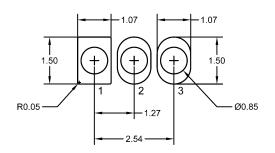

### **Suggested Pad Layout**

- 1. All linear dimensions are in millimeters.

- 2. Package weight approximately 0.12 grams

- 3. Molded plastic case UL 94V-0 rated

- For Tape and Reel specifications refer to InterFET CTC-021 Tape and Reel Specification, Document number: IF39002

- 5. Bulk product is shipped in standard ESD shipping material

- 6. Refer to JEDEC standards for additional information.

- 1. All linear dimensions are in millimeters.

- 2. The suggested land pattern dimensions have been provided for reference only. A more robust pattern may be desired for wave soldering.

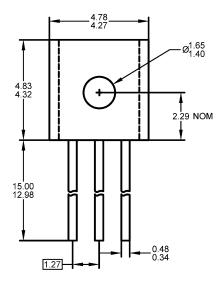

## **TO-92 Mechanical and Layout Data**

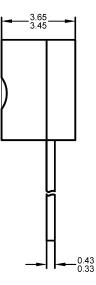

### Package Outline Data

### Suggested Through-Hole Layout

- 1. All linear dimensions are in millimeters.

- 2. Package weight approximately 0.19 grams

- 3. Molded plastic case UL 94V-0 rated

- 4. Bulk product is shipped in standard ESD shipping material

- 5. Refer to JEDEC standards for additional information.

- 1. All linear dimensions are in millimeters.

- 2. The suggested land pattern dimensions have been provided as a straight lead reference only. A more robust pattern may be desired for wave soldering and/or bent lead configurations.